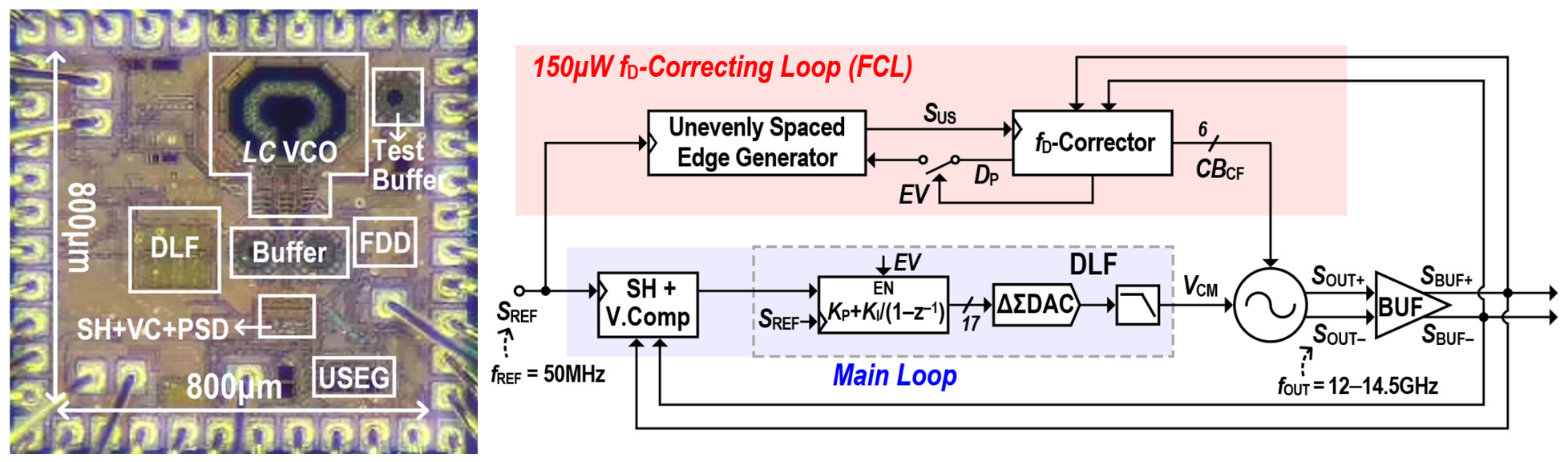

A 170MHz-Lock-In-Range and −253dB-FoMjitter 12-to-14.5GHz Subsampling PLL with a 150µW Frequency-Disturbance-Correcting Loop Using a Low-Power Unevenly Spaced Edge Generator

2021 IEEE International Solid- State Circuits Conference (ISSCC)

As the utilization of the mm-wave spectrum becomes active, designers’ interests are shifting to even higher frequencies in the W-band. Given their potential use as carrier frequencies for the next-generation mobiles (i.e., beyond 5G), these W-band signals must have ultra-low phase noise (PN). Currently, the most popular solution to generate such frequencies is with a cascaded architecture: a first-stage PLL generates a low-PN signal at a relatively low frequency at which the VCO LC tank has a high Q factor, and following frequency multipliers (FMs) increase the frequency to the W-band [1]. Although various FMs have been proposed, all of them are limited in their ability to achieve a high multiplication factor, M. Push-push or harmonic-selection circuits have high conversion losses. Injection-locked FMs (ILFMs) require multiple stages due to their narrow lock ranges, which increase power consumption and complexity. Thus, single-stage direct PLLs [2-4] would be preferred if they could have a sufficiently wide loop bandwidth to suppress the poor PN of a W-band VCO. Subsampling PLLs (SSPLLs) are suitable for extending the bandwidth since they have low in-band PN due to the high phase-error (φ ERR ) detection gain of a subsampling phase detector (PD). Nevertheless, when SSPLLs operate in the W-band, the degradation of PN is unavoidable because the φ ERR detection gain decreases as the frequency of the VCO, f VCO , increases. As described at the left of Fig. 23.4.1, when the switch of the PD, SWPD, is closed, the output of the PD, SPD, should track the signal of the VCO, S VCO , closely. However, when f VCO increases to the W-band, the amplitude of SPD is reduced significantly by a parasitic pole that is present due to the turned-on resistance of SW PD , R ON , and the sampling capacitor, CS. When SWPD is turned off, φ ERR is detected in SPD, but its magnitude is already suppressed significantly relative to that in SVCO. This effect also can be interpreted in the frequency domain where S VCO is suppressed by a low-pass filter before the information of φ ERR is extracted at the baseband frequencies.