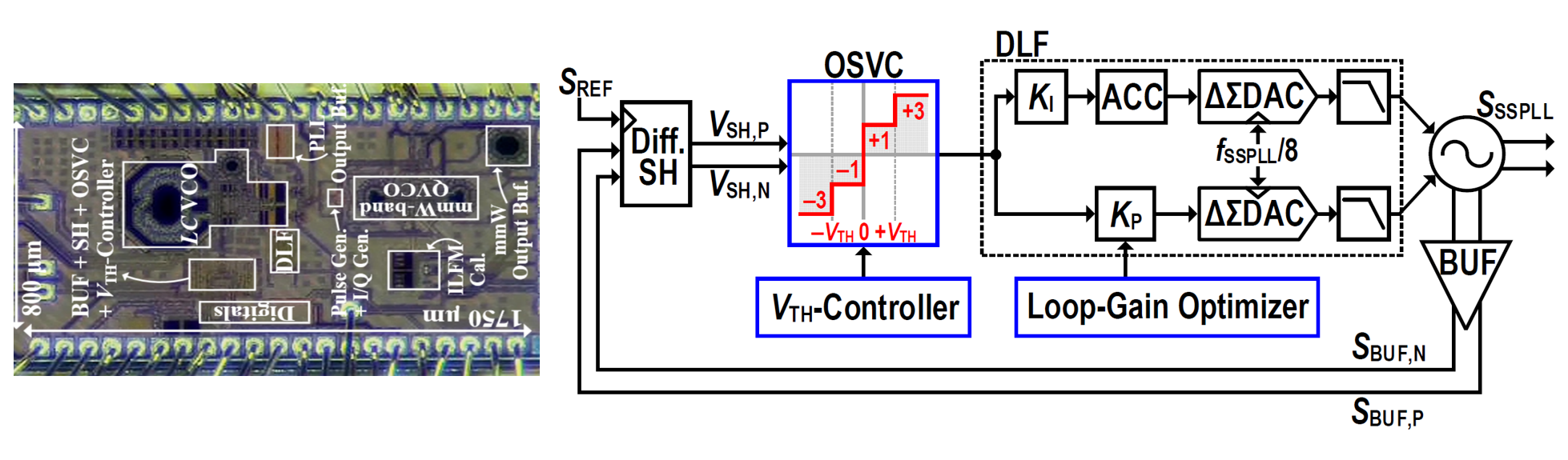

A 76fsrms Jitter and –40dBc Integrated-Phase-Noise 28-to-31GHz Frequency Synthesizer Based on Digital Sub-Sampling PLL Using Optimally Spaced Voltage Comparators and Background Loop-Gain Optimization

2021 IEEE International Solid- State Circuits Conference (ISSCC)

https://ieeexplore.ieee.org/document/8662532

IEEE Journal of Solid-State Circuits

The generation of mm-wave (mmW) signals that have ultra-low phase noise (PN) is very important for the design of RF transceivers (TRXs) for high-data-rate 5G systems. Direct-RF-sampling TRXs also require high-frequency clock signals, having extremely low integrated PN (IPN) [1]. To satisfy such stringent noise requirements, the rms jitter of mmW-band signals must be reduced to sub-100fs. Recently, a charge-pump (CP) PLL in [1] achieved a very low rms jitter of less than 60fs at 14GHz. However, to suppress the in-band PN of PLL building blocks, that design used a reference clock that had an impractically high frequency, f REF , of 500MHz. To avoid the use of such a high f REF while minimizing in-band PN, sub-sampling PLLs (SSPLLs) are seen as a promising solution. However, conventional SSPLLs are not suitable for generating mmW-band signals directly, since, as the frequency increases, the capture range of their sampling operation is reduced rapidly, thereby hindering the reliable operation. To extend the capture range, a prescaler can be used after the VCO [2], but it increases the in-band PN and power consumption. Direct-mmW SSPLLs are limited even at suppressing out-of-band PN, since their PN skirt is determined by an mmW VCO that has a relatively low Q. To overcome the problems of analog SSPLLs, such as a large area and a PVT-sensitive loop gain, digital SSPLLs using ADCs to digitize the sampled voltage have been developed recently [3]. However, digital SSPLLs suffer from another problem in that, to reduce the quantization noise (Q-noise) and improve the overall IPN, they must use high-performance ADCs that concurrently have high-sampling frequencies, fine resolutions, and wide dynamic ranges. Thus, they demand high power and occupy larger area.