A PVT-robust −59-dBc reference spur and 450-fsRMS jitter injection-locked clock multiplier using a voltage-domain period-calibrating loop

2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits)

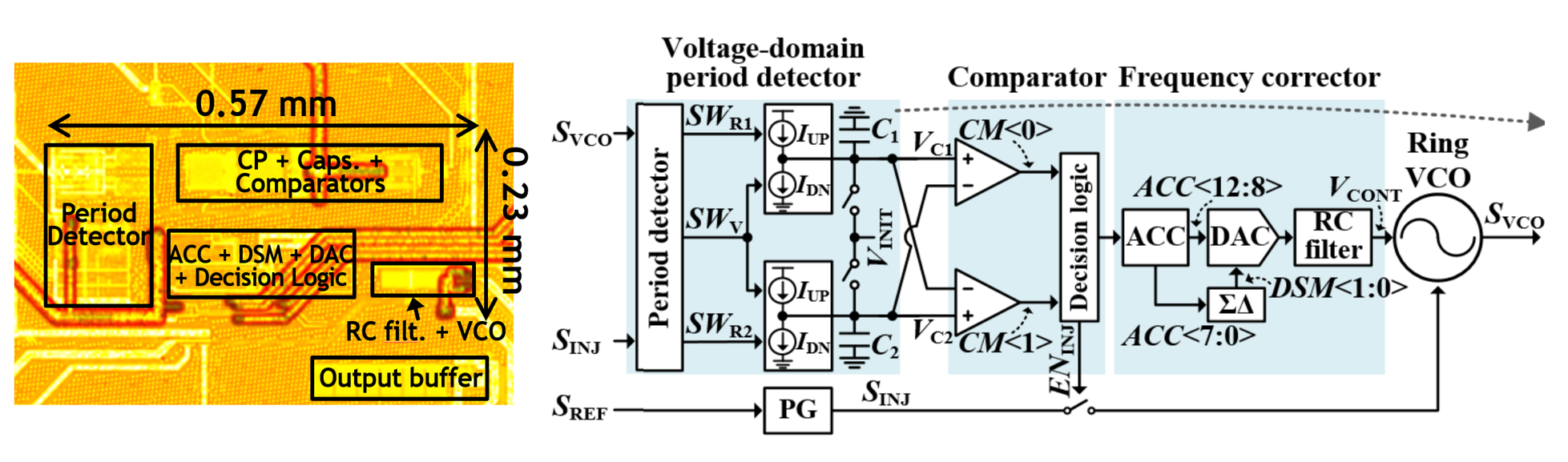

This paper presents a low-reference-spur and low-jitter injection-locked clock multiplier (ILCM). To secure these performances over PVT-variations, we propose the use of a voltage-domain period-calibrating loop (VDPCL) in the ILCM that monitors the intrinsic period of the VCO and stores this information as the charges in a capacitor. By evaluating the voltage of the capacitor, it is possible to correct the free-running frequency of the VCO. By iteratively accumulating charges, the precision of the calibration can be increased. The measured reference spur and RMS jitter were -59 dBc and 450 fs, respectively, and their degradations over the PVT were less than 1.5 dB and 50 fs, respectively.